In the fields of network and IT, each invention intends to resolve previously encountered issues. The one of these inventions is the PCIe bus. The PCIe (Peripheral Component Interconnect Express – commonly called PCI express) Bus, refers to the actual expansions slots on the PC’s motherboard that accept PCIe expansion boards. It is introduced to meet the needs of high bandwidth, high flexibility and its performances of network devices. Since its apperance, PCIe has been rapidly developed and widely applied in many network peripherals.

What is a PCI Express board ?

The PCI Express is a motherboard internal connection slot technology. It succeeds PCI and AGP. It’s a connector that is used to connect the expansion boards on the motherboard of a computer. So basically it is a bus that allows to exchange the data between the board and the rest of the peripherals of the computer.

How does the PCI Express board work ?

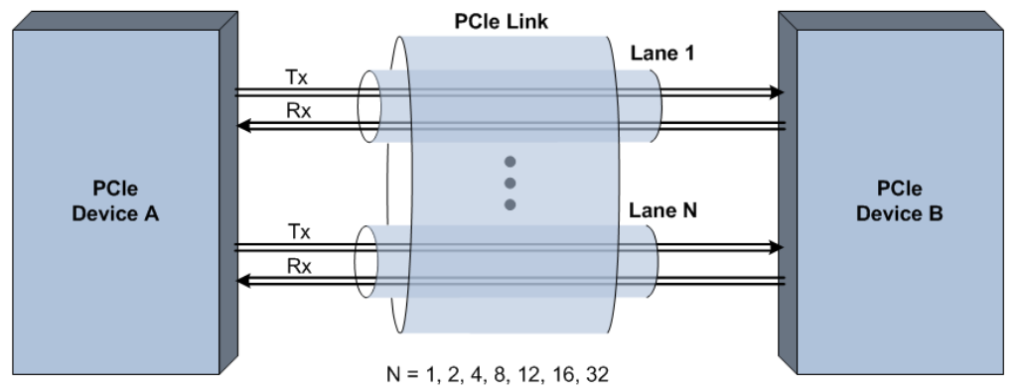

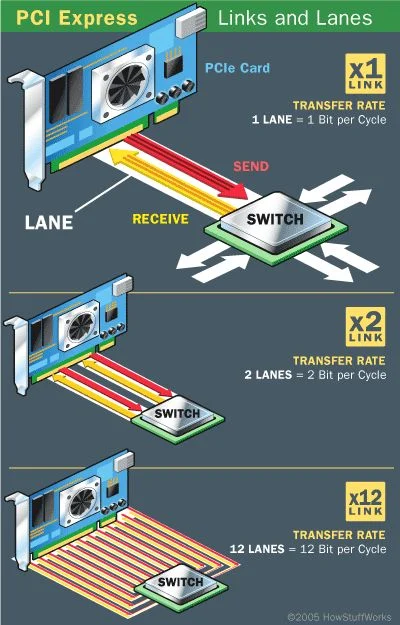

The PCIe board can realize a series of point-to-point connection through switches in order to control the direction of the data direction instead of operating as a bus that handles data from multiple sources. After inserting a PCIe netword board, a logical connection will be established between the slot to communicate. This connection, called interconnection or link, allows a point-to-point communication channel between two PCIe ports, and allows them to send and receive ordinary PCI request and interrupts. As you can see the figure below illustrates the PCIe slot contains more lanes. It is posssible for PCIe to contain one lane too.. A PCIe link is made up of one or more lanes to “Transmit and Receive’ the data through differential pair. It can support x1, x2, x4, x6, x12, x16, x32 lanes/link enables a scalable bandwidth to meet the needs of a wide variety of applications.

Finally the PCIe bus gives the possibility to two PCIe boards to communicate between them bypassing the PC procesor, which was not possible before.

Neverthless, a PCIe x4 port can have the same number of pins as a PCIe x16 without having the sufficient number of lanes. Thus, the PCIe x4 port may look like a PCI x16 port when ultimately operating with much less bandwidth. That’s what is indicated in the PCIe 3.0 x16 x4 specification.

The number of lanes affects the speed and bandwidth. The more lanes there are, the greater the flow.

PCI Express Bandwidth and Speeds

Here is the speed comparison, bandwidth according to generation and the lane numbers. A single lane of PCI Express can handle 250 MByte of traffic in each direction per second. Each lane and generation multiplies the flow by 2 (x2). In table below there are some data about PCI Express and its versions with badwidth.

| Number of lane | PCIe 1.0 | PCIe 2.0 | PCIe 3.0 | PCIe 4.0 | PCIe 5.0 | PCIe 6.0 |

| x1 | 250 MB/s | 500MB/s | 1GB/s | 2GB/s | 4GB/s | 8GB/s |

| x2 | 500MB/s | 1GB/s | 2GB/s | 4GB/s | 8GB/s | 16GB/s |

| x4 | 1GB/s | 2GB/s | 4GB/s | 8GB/s | 16GB/s | 32GB/s |

| x8 | 2GB/s | 4GB/s | 8GB/s | 16GB/s | 32GB/s | 64GB/s |

| x16 | 4GB/s | 8GB/s | 16GB/s | 32GB/s | 64GB/s | 128GB/s |

The PCIe applications at LaRocheNoire Technology

At LaRocheNoire Technolgy, we use the PCI Express to interconnect different FPGA based boards on the same backplane. The FPGA based boards could interact with each other without the need for external intervention. Therefore, the PCI Express used in our products are controlled by a processor on the backplanes to collect the data and monitor the communication between boards.